Gerbang logika atau gerbang logik adalah suatu entitas dalam elektronika dan matematika Boolean yang mengubah satu atau beberapa masukan logik menjadi sebuah sinyal keluaran logik. Gerbang logika terutama diimplementasikan secara elektronis menggunakan dioda atau transistor, akan tetapi dapat pula dibangun menggunakan susunan komponen-komponen yang memanfaatkan sifat-sifat elektromagnetik (relay), cairan, optik dan bahkan mekanik.

Jenis- jenis Gerbang Logika :

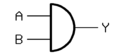

GERBANG AND

Gerbang AND dapat memiliki dua masukan atau lebih. Gerbang ini akan menghasilkan keluaran 1 hanya apabila semua masukannya sebesar 1. Dengan kata lain apabila salah satu masukannya 0 maka keluarannya pasti 0.

Sebagai contoh, perhatikanlah kasus berikut:

Kasus

Sebuah tim ganda dari regu bulutangkis Indonesia, adalah absah apabila kedua

anggotanya lengkap hadir, yaitu Amir dan Badu. Apabila salah satu dari Amir atau Badu ada yang absen atau tidak hadir, maka regu tersebut tidak absah untuk Mewakili Indonesia dalam turnamen bulu tangkis tersebut.

Dalam dunia logika digital, semua aspek positif dari suatu kasus diinterpretasikan sebagai true (baca: tru) suatu kata bahasa Inggris yang berarti 'benar'. Pada komputer (sebagai perangkat), 'true' diwujudkan sebagai logika '1' atau 'high' (baca: hay') = tinggi. Pada tingkat perangkat keras, 'true' mempunyai acuan tegangan listrik mendekati 5 Volt DC (dalam TTL Level).}

Pada kasus di atas, yang termasuk aspek positif adalah 'absah' dan 'hadir'. Sebaliknya, logika digital menentukan bahwa semua aspek negatif dalam suatu kasus harus dianggap sebagai false (baca: fals) yang berarti 'salah'. Ini dimanifestasikan sebagai logika '0' atau low = rendah oleh komputer (sebagai perangkat). Perangkat keras melaksanakan hal ini dengan memberikan tegangan DC mendekati atau sama dengan nol Volt, TTL level.

Yang termasuk aspek negatif dalam hal ini adalah 'tidak absah' dan 'absen'. Dengan demikian, kita sudah dapat menjabarkan kasus tersebut secara logika seperti ini:

a. Penyelesaian (output) kasus disandikan dengan 'Q'.

b. Peserta (input), dalam hal ini Amir dan Badu, disandikan sebagai A dan B.

c. Sinopsis yang dihasilkan menyatakan bahwa:

- Q akan true apabila A dan B true

- Q akan false bila salah satu di antara A dan B ada yang false

Bentuk logika kasus diatas disebut logika 'AND', yang dalam bahasa Indonesia berarti 'DAN'. Tampaknya, nama logika ini diperoleh dengan mengambil patokan pada sinopsis bagian pertama, yang menyatakan bahwa output akan true bila A dan B true.

Tabel Kebenaran:

Tabel Kebenaran:

| A | B | Y |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

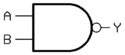

GERBANG NAND (NOT AND)

Berlawanan dengan gerbang AND, pada gerbang NAND keluaran akan selalu 1 apabila salah satu masukannya 0. Dan keluaran akan sebesar 0 hanya apabila semua masukannya 1.

Gerbang NAND ekuivalen dengan NOT AND.

Tabel Kebenaran:

Tabel Kebenaran:

| A | B | Y |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

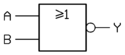

GERBANG OR

Keluaran gerbang OR akan sebesar 0 hanya apabila semua masukannya 0. Dan keluarannya akan sebesar 1 apabila ada salah satu masukannya yang bernilai 1.

Sebagai contoh, perhatikanlah kasus berikut:

Kasus

Dalam suatu rapat Universitas, Amir dan badu bertindak sebagai wakil resmi Fakultas Teknik jurusan elektro. Sidang rapat menyatakan apabila salah satu dari Amir atau Badu hadir, maka hal itu sudah absah untuk mewakili fakultas tersebut.

Untuk kasus ini, penjabaran masalah tidak banyak berbeda dengan yang sebelumnya yaitu:

a. Penyelesaian (output) kasus disandikan dengan 'Q'.

b. Peserta (input), dalam hal ini Amir dan Badu, disandikan sebagai A dan B.

c. Sinopsis yang dihasilkan menyatakan bahwa:

- Q akan true apabila salah satu dari A dan B ada dalam kondisi true.

- Q akan false, apabila A dan B (semuanya) ada dalam keadaan false.

Tabel Kebenaran :

Tabel Kebenaran :

| A | B | Y |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

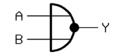

GERBANG NOR (NOT OR)

Gerbang NOR ekuivalen dengan NOT OR. Berlawanan dengan gerbang OR, keluaran sebesar 1 hanya akan terjadi apabila semua masukannya sebesar 0. Dan keluaran 0 akan terjadi apabila terdapat masukan yang bernilai 1. Tabel kebenaran gerbang NOR.

Tabel Kebenaran:

Tabel Kebenaran:

| A | B | Y |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

GERBANG NOT

Pada gerbang ini nilai keluarannya selalu berlawanan dengan nilai masukannya. Apabila masukannya sebesar 0 maka keluarannya akan sebesar 1 dan sebaliknya apabila masukannya sebesar 1 maka keluarannya akan sebesar 0.

Tabel Kebenaran:

Tabel Kebenaran:

| A | Y |

|---|---|

| 0 | 1 |

| 1 | 0 |

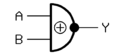

Apabila input A dan B ada dalam keadaan logika yang sama, maka output Q akan menghasilkan logika 0, sedangkan bila input A dan B ada dalam keadaan logika yang berbeda, maka output akan menjadi logika 1. XOR sebetulnya merupakan variasi dari cara kerja logika OR.

Tabel kebenaran XOR ini hanya berbeda satu langkahsaja dengan tabel kebenaran OR, yaitu pada langkah terakhir saat input A dan B keduanya pada logika 1, outputnya menghasilkan 0, bukan 1 seperti pada logika OR.

Aplikasi dari proses logika XOR ini dapat dimanfaatkan untuk membandingkan dua buah data, yaitu apabila data-data tersebut mengandung informasi yang persis sama, maka XOR akanmemberikan output logika 0.

Tabel Kebenaran:

Tabel Kebenaran:

| A | B | Y |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

GERBANG XNOR (Exclusive NOR)

Apabila input A dan B ada dalam keadaan logika yang sama, maka output Q akan menghasilkan logika 1, sedangkan bila input A dan B ada dalam keadaan logika yang berbeda, maka output akan menjadi logika 0. XNOR bisa juga dikatakan memiliki sifat dari kebalikan XOR. XNOR dan NOR hanyalah berbeda pada langkah ke-empat yaitu apabila A dan B pada logika 1 maka output Q juga 1, bukan 0 seperti pada logika NOR.

Tabel Kebenaran:

Tabel Kebenaran:

| A | B | Y |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

| Nama | Fungsi | Lambang dalam rangkaian | ||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| IEC 60617-12 | US-Norm | DIN 40700 (sebelum 1976) | ||||||||||||||||||

| Gerbang-AND (AND) |    |  |  |  | ||||||||||||||||

| Gerbang-OR (OR) |   |  |  |  | ||||||||||||||||

| Gerbang-NOT (NOT, Gerbang-komplemen, Pembalik(Inverter)) |   |  |  |  | ||||||||||||||||

| Gerbang-NAND (Not-AND) |    |  |  |  | ||||||||||||||||

| Gerbang-NOR (Not-OR) |    |  |  |  | ||||||||||||||||

| Gerbang-XOR (Antivalen, Exclusive-OR) |   |  |  |  atau  | ||||||||||||||||

| Gerbang-XNOR (Ekuivalen, Not-Exclusive-OR) |   |  |  |  atau  | ||||||||||||||||

3 Comment:

ramudheng babar blas aku dhik.! (doh)

apa sih manfaat gerbang logika itu ....

tolong berika penjelasan dan contoh kasusnya ?

gerbang logika hanyalah logika hardware di dalam IC yang nantinya akan diubah BIOS ke bahasa OS yang "people friendly". untuk lebih jelasnya baca di wikipedia saja

Posting Komentar

nek arep komentar ndang ditulis cepet!